# Specifying, Verifying, and Translating Between Memory Consistency Models

DANIEL JOSEPH LUSTIG

A Dissertation Presented to the Faculty of Princeton University in Candidacy for the Degree of Doctor of Philosophy

Recommended for Acceptance by the Department of Electrical Engineering Adviser: Professor Margaret Martonosi

November 2015

$\bigodot$  Copyright by Daniel Joseph Lustig, 2015.

All rights reserved.

### Abstract

Gone are the days when single-threaded performance was the primary metric of interest for a processor design. Driven by increasingly tight power constraints and by the slowing down of Moore's law and Dennard scaling, architects have turned to multicore parallelism and architectural heterogeneity as a means to continue delivering increases in chip performance and power efficiency. Both approaches can deliver improved performance per watt characteristics at the expense of creating systems which are dramatically more complex to design and harder to program.

In order to share data and coordinate their actions, the compute elements (e.g., CPU cores, GPU cores, accelerators) in modern processors communicate via *shared* virtual memory. In this model, regardless of the underlying physical reality, cores see the abstraction of a single unified address space shared with the other processing elements in the system. Communication through shared virtual memory takes place according to a memory consistency model—the set of rules and guarantees about the ordering and visibility of memory accesses issued by one processing element and observed by other processing elements. Unfortunately, in practice, hardware consistency model definitions frequently suffer from a lack of formalism, precision, and/or completeness, resulting in numerous situations in which the correct outcome(s) for a given scenario may be ambiguous or even simply undefined. To solve these problems, this thesis develops formal analysis techniques, specification formats, and automated tools that aim to mitigate the problems of incompleteness, imprecision, and/or incompatibility among memory consistency models.

First, this thesis proposes Memory Ordering Specification Tables (MOSTs), a systematic method for fully and explicitly enumerating the memory ordering requirements of axiomatic memory models. The architecture- and model-independent approach used by the MOST format allows for the direct comparison of preserved program order, fences, and other ordering enforcement mechanisms from the same or even from different models. In particular, it allows for the direct comparison of models that are weakly-ordered (e.g., ARM, IBM Power, GPUs), strongly-ordered (e.g., sequential consistency, SPARC/x86 Total Store Ordering), or points in between. This thesis also presents the ArMOR framework for systematically analyzing and manipulating MOSTs. As a demonstration of the power of ArMOR, this thesis presents a methodology for automatically and dynamically translating code compiled under the assumptions of one memory model into code which can be executed by a (micro)architecture implementing a different memory model. By analyzing MOSTs for the source and destination architectures, ArMOR analysis can be used to produce optimized, self-contained translation engines called *shims*. The shim designs can be derived offline and in advance, and they can be easily implemented in software or hardware with manageable performance overhead.

Second, this thesis proposes PipeCheck, a framework for verifying the correctness of particular implementations of a given architectural memory model. PipeCheck defines a domain-specific language for specifying memory ordering behavior at the microarchitecture level. This language allows PipeCheck to explicitly specify and verify the behavior of common microarchitectural optimizations such as speculative load reordering which are intentionally abstracted away by higher-level models. PipeCheck's fast constraint solver software quantifies in just minutes whether an implementation is stronger than, weaker than, or equal in strength to its memory model requirements. It also reduces a currently intractable problem—verifying register transfer level (RTL) hardware descriptions against architectural memory model requirements—into a much more tractable task: verifying RTL against a set of locallyscoped, per-pipeline stage ordering properties. This thesis applies PipeCheck at a number of locations within a processor: within the pipeline, within the cache coherence protocol, and at the coherence/consistency interface, and it demonstrates the practicality of rigorously analyzing a broad range of microarchitectural scenarios. In summary, this thesis presents architects with new techniques for reducing the complexity of defining memory consistency models and building systems that correctly implement them. In doing so, it narrows the existing gap between performance-first architectural design methodologies and rigorous verification of implementation correctness. As hardware and software complexity and dynamism continue to grow, the techniques developed in this thesis will help designers avoid the memory model bugs that continue to appear in hardware even today, and they will present programmers, compiler writers, and runtime systems with usable, precise descriptions of the memory ordering behaviors of any simple or complex computing system.

### Acknowledgements

It's hard to believe that my time at Princeton is coming to an end. It was an amazing experience, and I can't help but acknowledge all of the help and friendship I received from so many people over my years here. None of this would have been possible without all of their support and guidance, and I'm going to do my best to thank them all here.

First of all, I would like to give enormous thanks to my adviser Margaret Martonosi. I couldn't have asked for anything more from an adviser. She helped guide me through the highs and the lows of my Ph.D., and she always pushed me to improve in all aspects of my career. She was always there for me whenever I needed advice, whether it be technical, professional, personal, or otherwise. She accepted nothing less than my best, and I will be forever grateful for her mentorship.

I would also like to thank the rest of my thesis committee: Andrew Appel, Sharad Malik, Michael Pellauer, and David Wentzlaff. Their feedback, suggestions, and mentorship made this thesis possible. I would especially like to thank Michael Pellauer for all of his support and guidance during my internships and during my time back at Princeton. Michael went out of his way to keep our collaborations going strong, and his input really helped my Ph.D. start to take shape. I'm extremely thankful that he was willing to make time for our weekly meetings and frequent emails, even through a change in employers.

I'd also like to thank all of the other members of the former VSSAD, especially Joel, Angshu, Aamer, Neal, Michael, Elliott, Bushra, and Mohit. Joel Emer was an excellent mentor to me during my three internships with the group, and I'm grateful for his support during and after my time there. I'm really looking forward to working with many of them again at NVIDIA.

Abhishek Bhattacharjee has been an amazing friend and mentor to me since the day I joined MRMGroup. From the beginning, he taught me what it means to be a Ph.D. student and an academic, and I'm infinitely better off for having him as someone I can trust and count on for advice. I'm really glad we got to start working together again, and I hope there's more where that came from in the future.

In addition, I have to give huge thanks to all of the other members of MRMGroup: Sibren, Carole, Wenhao, Yavuz, Ozlem, Ali, Tae Jun, Logan, Elba, Caroline, Yatin, Themis, Shruti, Daeki, and Geet. They made it fun to be in the office every day, and we shared so many thoughts, laughs, lunches, insights, and stories that it's hard to even remember them all. I also have to give a shoutout to the Malik group members, the Wentzlaff group members, the reading group members, and everyone else with whom I've worked and become friends during my time at Princeton.

I've benefited tremendously from other collaborations and interactions as well. Thanks to Kevin Skadron, Kelly Shaw, and Ke Wang for their help during our earlier teleconferences. Thanks also to the staffs of the Electrical Engineering and Computer Science departments for helping me through the logistics of the program. I'd especially like to thank Lori Bailey and Stacey Weber Jackson for being so friendly and helpful with anything I ever asked of them.

A very special thank you goes to my wonderful girlfriend, Sunha Ahn. Since that first EE holiday party we attended, we shared so many special and important moments together, at Princeton and around the world. We made each other laugh, we supported each other throughout the bad times, and we celebrated together during the good times. She kept me motivated, and she kept me focused on what is really important in life. I couldn't have made it through my Ph.D. without her.

Finally, I would like to extend a huge thank you to everyone on both sides of my family. First and foremost, I have to thank my parents for channeling my interests in math and science into a successful career path, for making the sacrifice to send me to Loyola and to Penn, and for the endless and uninterrupted love and support. I also have to thank so many others: David, Mamá, Papá, Martha, Laura, John, Brad, Reagan, Carmen, and the hundreds of other actual and honorary Cubans that were behind me all the way. On the other side, I would like to thank Grandpa, Marion, Josh, Patty, Ashley, Sharon, Jessica, Adam, and Bryan for being there for me as well. I am extremely lucky to have come from such a huge and loving extended family. I am also extremely lucky to have benefited from their decisions to escape bad situations across the world to make better lives for themselves and for their families here in America. Their love and their sacrifices allowed me to get where I am today, and for that reason, I dedicate this thesis to them.

To my parents.

# Contents

| Abst | tract .                                                       |                                                                                                                                                                                                                                                                                                                                                                          | iii                                                  |

|------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Ack  | nowledg                                                       | ements                                                                                                                                                                                                                                                                                                                                                                   | vi                                                   |

| Intr | oducti                                                        | on                                                                                                                                                                                                                                                                                                                                                                       | 1                                                    |

| 1.1  | Motiva                                                        | tion                                                                                                                                                                                                                                                                                                                                                                     | 1                                                    |

| 1.2  | Resear                                                        | ch Challenges and Goals                                                                                                                                                                                                                                                                                                                                                  | 5                                                    |

| 1.3  | Definir                                                       | ng Memory Models in an Architecture-Independent Manner $\ .$ .                                                                                                                                                                                                                                                                                                           | 7                                                    |

|      | 1.3.1                                                         | Dynamic Migration Between Consistency Models                                                                                                                                                                                                                                                                                                                             | 8                                                    |

| 1.4  | Microa                                                        | architecture-Level Memory Consistency Models                                                                                                                                                                                                                                                                                                                             | 9                                                    |

|      | 1.4.1                                                         | Pipeline Models                                                                                                                                                                                                                                                                                                                                                          | 11                                                   |

|      | 1.4.2                                                         | Cache and Memory System Models                                                                                                                                                                                                                                                                                                                                           | 11                                                   |

|      | 1.4.3                                                         | Address Translation                                                                                                                                                                                                                                                                                                                                                      | 12                                                   |

| 1.5  | Thesis                                                        | Contributions                                                                                                                                                                                                                                                                                                                                                            | 12                                                   |

| 1.6  | Thesis                                                        | Outline                                                                                                                                                                                                                                                                                                                                                                  | 13                                                   |

| Bac  | kgroun                                                        | d and Related Work                                                                                                                                                                                                                                                                                                                                                       | 15                                                   |

| 2.1  | Basic (                                                       | Overview                                                                                                                                                                                                                                                                                                                                                                 | 15                                                   |

|      | 2.1.1                                                         | From Sequential Consistency to Weak Ordering                                                                                                                                                                                                                                                                                                                             | 16                                                   |

|      | 2.1.2                                                         | A Stack of Memory Consistency Models                                                                                                                                                                                                                                                                                                                                     | 20                                                   |

|      | 2.1.3                                                         | Coherence vs. Consistency                                                                                                                                                                                                                                                                                                                                                | 20                                                   |

|      | 2.1.4                                                         | Litmus Tests                                                                                                                                                                                                                                                                                                                                                             | 23                                                   |

|      | Acka<br>Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>Bac | Ack-owledge         Introduction         1.1       Motivand         1.2       Researd         1.3       Definition         1.3       Definition         1.3       Definition         1.4       Microard         1.4.1       1.4.2         1.4.3       1.4.3         1.5       Thesis         1.6       Thesis         2.1       Basic of 2.1.1         2.1.2       2.1.3 | <ul> <li>1.2 Research Challenges and Goals</li></ul> |

|   | 2.2 | Defini | ng Weak Memory Models                         | 24 |

|---|-----|--------|-----------------------------------------------|----|

|   |     | 2.2.1  | Motivating Example                            | 24 |

|   |     | 2.2.2  | Operational vs. Axiomatic Models              | 27 |

|   |     | 2.2.3  | Defining Models Which Reflect Actual Hardware | 29 |

|   |     | 2.2.4  | Other Subtle Ordering Relationships           | 32 |

|   | 2.3 | Empir  | rical Analysis of Memory Models               | 37 |

|   |     | 2.3.1  | Correctness                                   | 38 |

|   |     | 2.3.2  | Performance                                   | 39 |

|   | 2.4 | Comp   | aring and Mapping Between Models              | 40 |

|   | 2.5 | Simpli | ifying Abstractions Made in This Thesis       | 43 |

|   | 2.6 | Chapt  | er Summary                                    | 44 |

| 3 | Мо  | mory ( | Ordering Specification Tables and ArMOR       | 45 |

| 0 |     | -      |                                               |    |

|   | 3.1 |        |                                               | 45 |

|   | 3.2 | Motiv  | ating Example                                 | 47 |

|   | 3.3 | Memo   | ry Ordering Specification Tables              | 51 |

|   |     | 3.3.1  | Store Atomicity and Ordering Strength         | 51 |

|   |     | 3.3.2  | Same-Address Dependencies                     | 53 |

|   |     | 3.3.3  | Fence Cumulativity                            | 55 |

|   |     | 3.3.4  | Summary                                       | 56 |

|   | 3.4 | ArMC   | OR: Comparing and Manipulating MOSTs          | 56 |

|   |     | 3.4.1  | MOST Partition Refinement                     | 56 |

|   |     | 3.4.2  | ArMOR Comparison Operators                    | 58 |

|   |     | 3.4.3  | ArMOR Comparison Examples                     | 60 |

|   | 3.5 | Relate | ed Work                                       | 62 |

|   | 3.6 | Chapt  | er Summary                                    | 64 |

| 4 | Dyr | namic Translation Between Memory Consistency Models            | 65  |

|---|-----|----------------------------------------------------------------|-----|

|   | 4.1 | Introduction                                                   | 65  |

|   | 4.2 | Motivating Example                                             | 67  |

|   | 4.3 | Cross-MCM Dynamic Binary Translation                           | 69  |

|   |     | 4.3.1 High-Level Operation                                     | 69  |

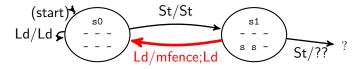

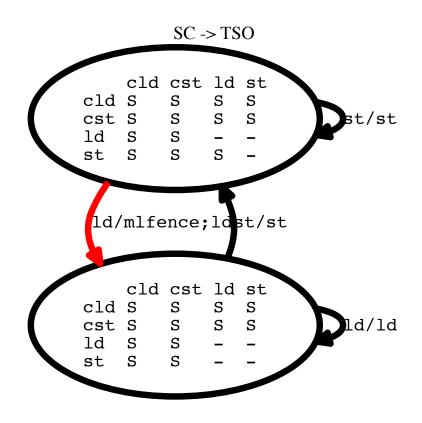

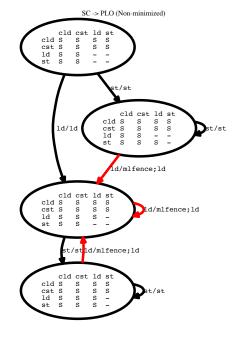

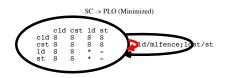

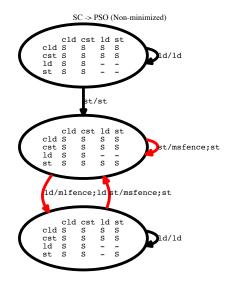

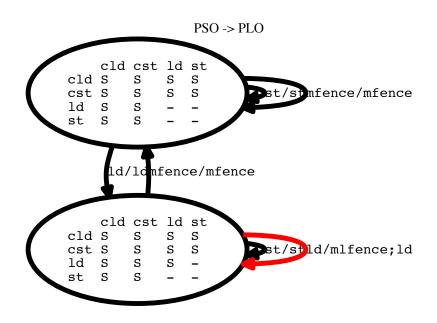

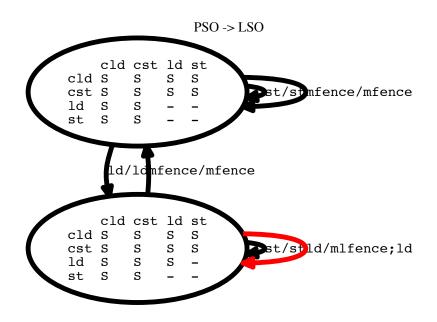

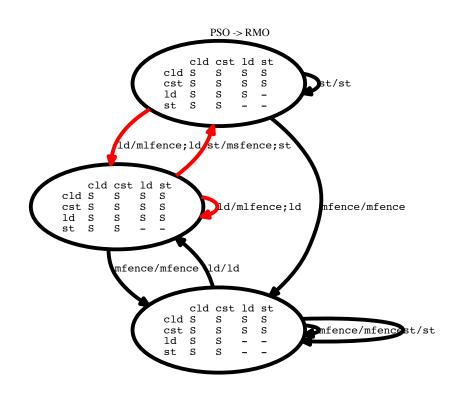

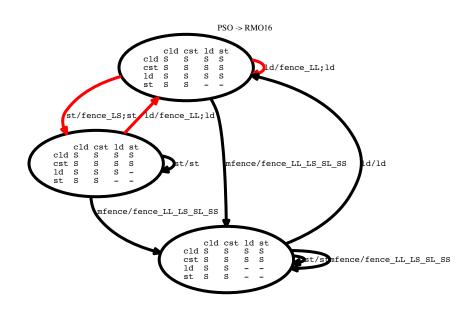

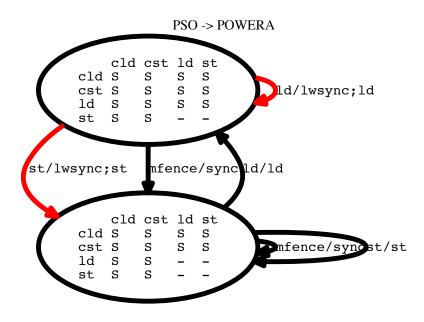

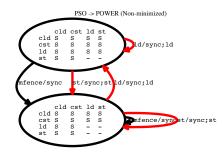

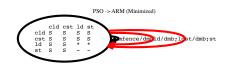

|   |     | 4.3.2 Shim Finite State Machines: Overview                     | 70  |

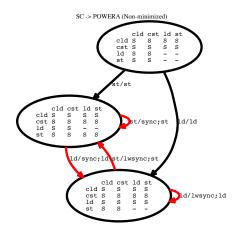

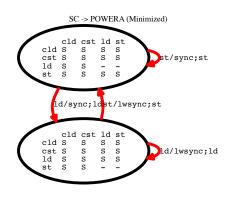

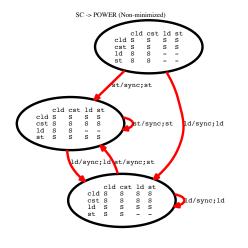

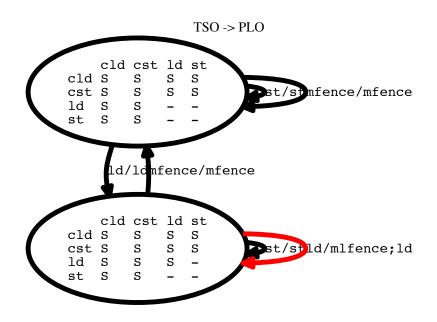

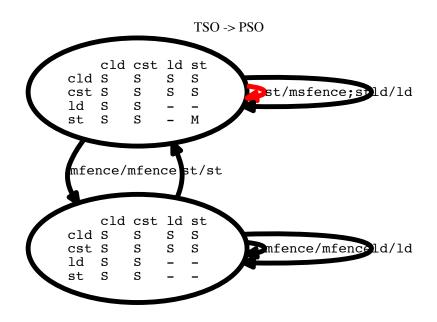

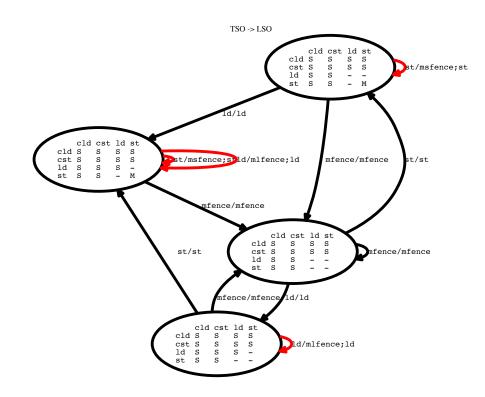

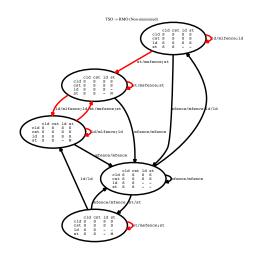

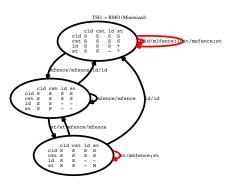

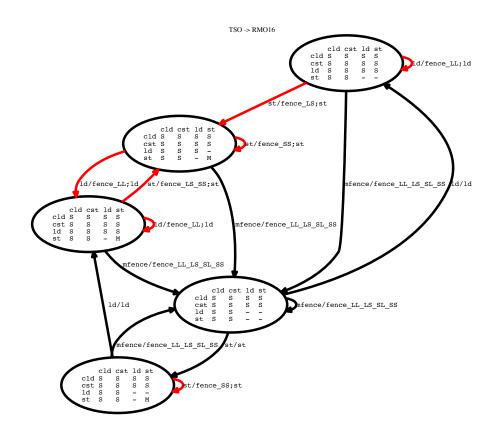

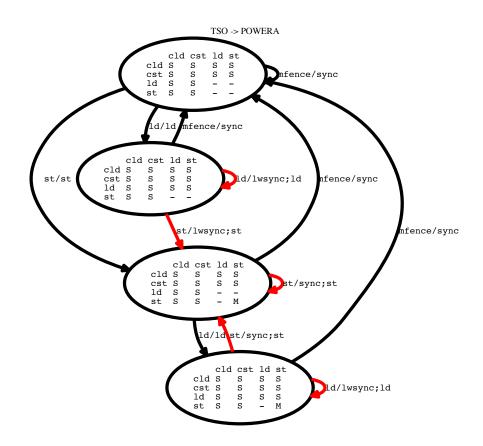

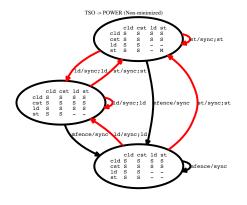

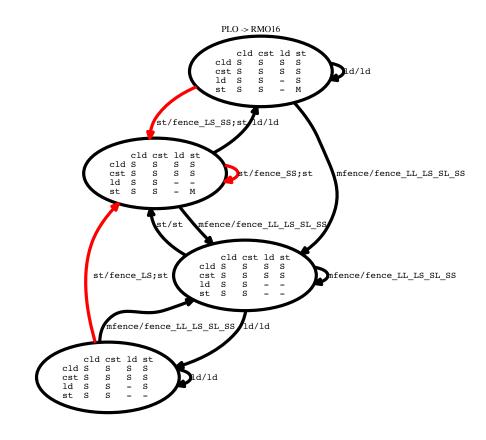

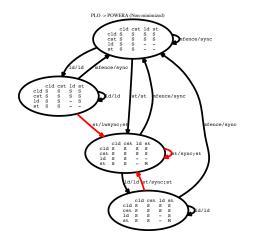

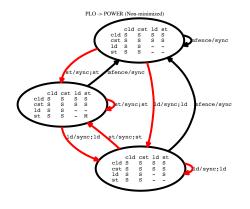

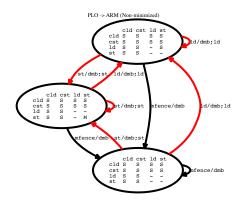

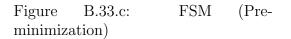

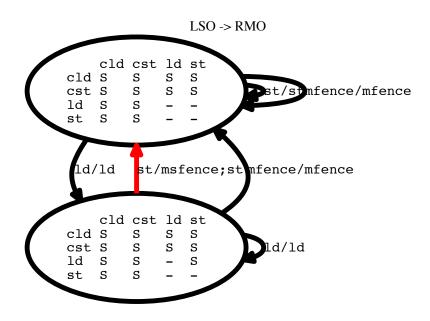

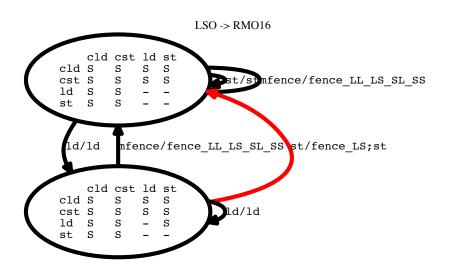

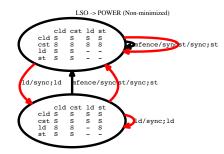

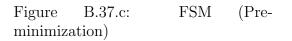

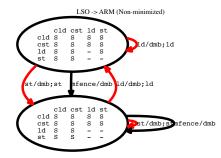

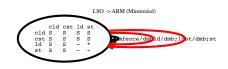

|   |     | 4.3.3 Shim FSM Generation                                      | 73  |

|   |     | 4.3.4 Shim FSM Generation Example                              | 78  |

|   |     | 4.3.5 Design Considerations                                    | 79  |

|   | 4.4 | Evaluation Methodology                                         | 83  |

|   |     | 4.4.1 Pintool-Based Exploration Methodology                    | 83  |

|   |     | 4.4.2 Hardware Simulation Methodology                          | 85  |

|   | 4.5 | Experimental Results                                           | 87  |

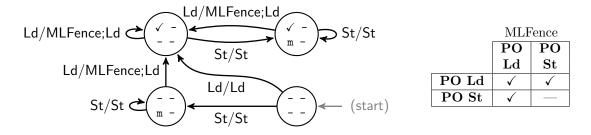

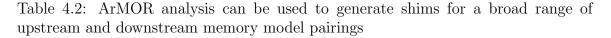

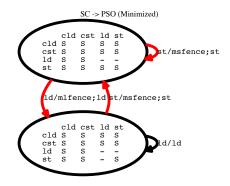

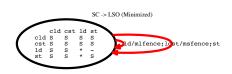

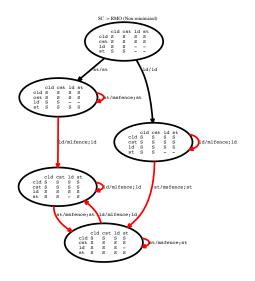

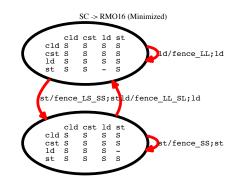

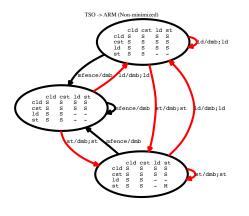

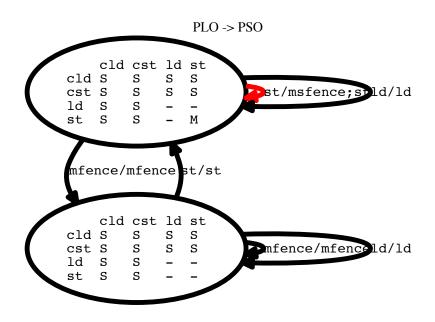

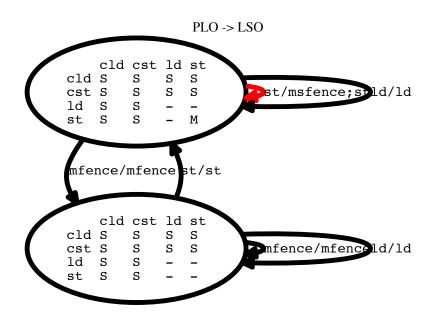

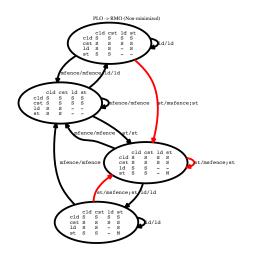

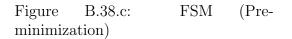

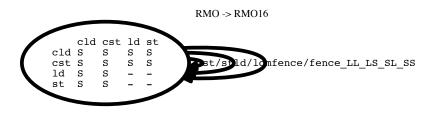

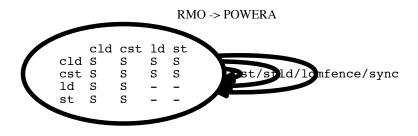

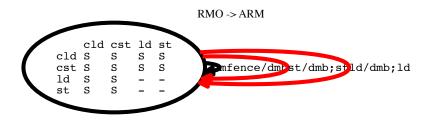

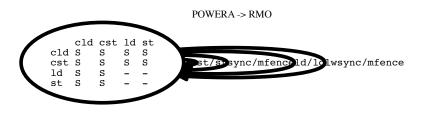

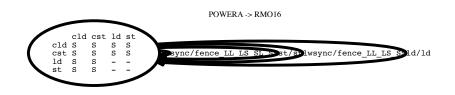

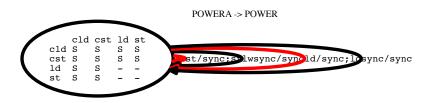

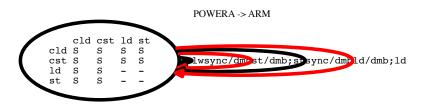

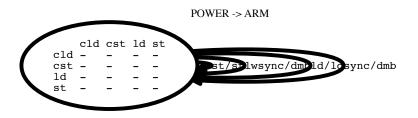

|   |     | 4.5.1 Shims for a Broad Range of Scenarios                     | 87  |

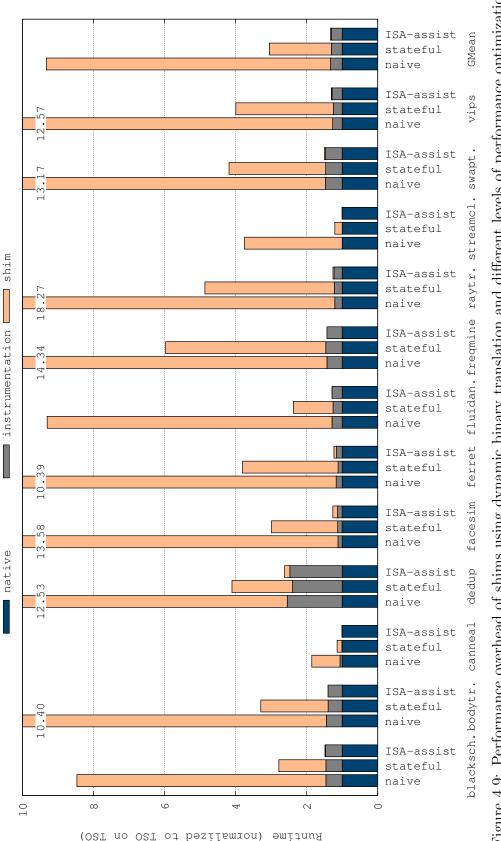

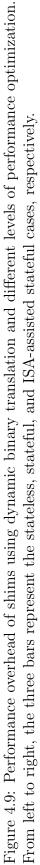

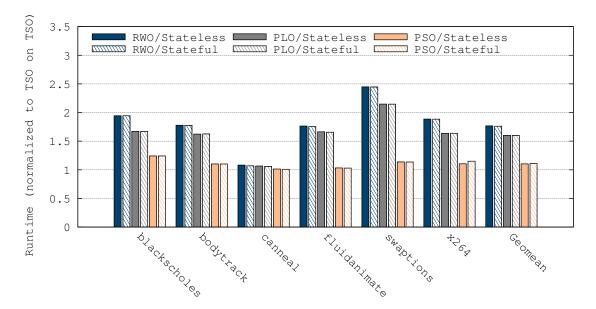

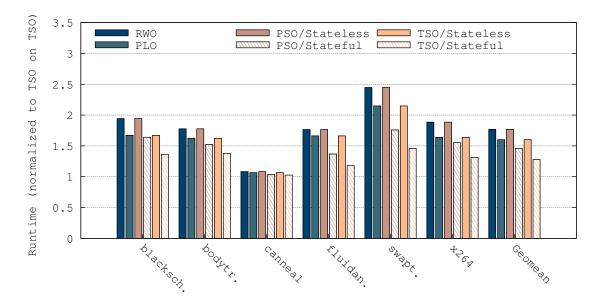

|   |     | 4.5.2 Performance of Software Shim Implementations             | 89  |

|   |     | 4.5.3 Performance of Hardware Shim Implementations             | 92  |

|   | 4.6 | Takeaways                                                      | 93  |

|   | 4.7 | Related Work                                                   | 95  |

|   | 4.8 | Chapter Summary                                                | 96  |

| 5 | Pip | eCheck: Specifying and Verifying Microarchitectural Enforce-   |     |

|   | mer | nt of Memory Consistency Models                                | 97  |

|   | 5.1 | Introduction                                                   | 97  |

|   | 5.2 | Motivating Example                                             | 99  |

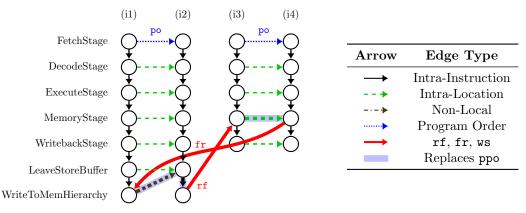

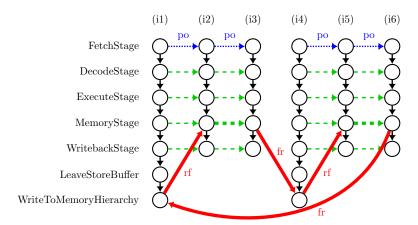

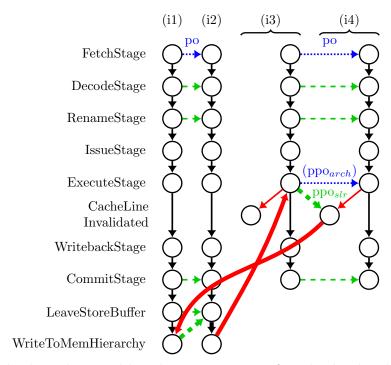

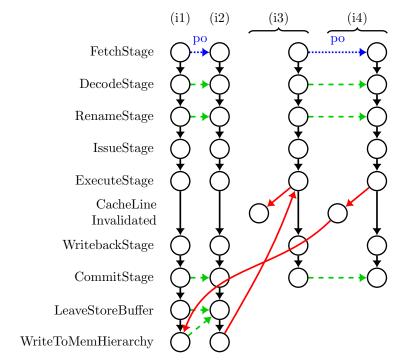

|   |     | 5.2.1 Microarchitecture-Level Analysis                         | 101 |

|   |     | 5.2.2 Deriving Correctness from Microarchitecture-Level Axioms | 104 |

|   | 5.3 | PipeCheck Microarchitecture-Level Analysis                     | 105 |

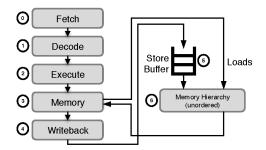

|   |     | 5.3.1 Microarchitecture Definition                             | 106 |

|   |     | 5.3.2   | PipeCheck Model Specification Language           | 109 |

|---|-----|---------|--------------------------------------------------|-----|

|   |     | 5.3.3   | Transitivity of $\mu hb$ Edges                   | 115 |

|   |     | 5.3.4   | Modeling Microarchitectural Optimizations        | 118 |

|   | 5.4 | Verific | eation Flow                                      | 120 |

|   |     | 5.4.1   | Litmus Test-Based Verification                   | 120 |

|   |     | 5.4.2   | Automated Constraint Solver Algorithm            | 124 |

|   |     | 5.4.3   | Software Implementation                          | 129 |

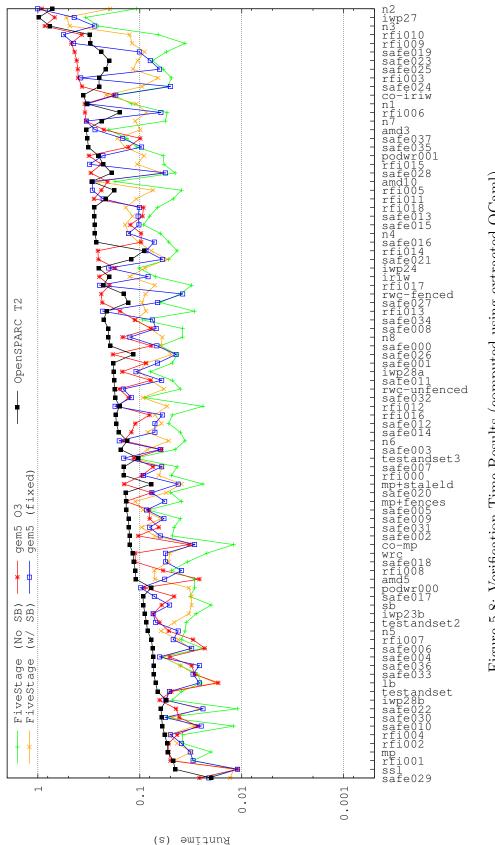

|   |     | 5.4.4   | Runtime                                          | 130 |

|   |     | 5.4.5   | Caveats                                          | 130 |

|   |     | 5.4.6   | Future Work: Formal Equivalence/Implication      | 131 |

|   | 5.5 | Exper   | imental Methodology                              | 132 |

|   | 5.6 | Result  | ts Across Litmus Tests                           | 133 |

|   | 5.7 | Case S  | Studies                                          | 136 |

|   |     | 5.7.1   | Speculative Load Reordering                      | 137 |

|   |     | 5.7.2   | Consistency Bug in gem5 O3 Pipeline              | 138 |

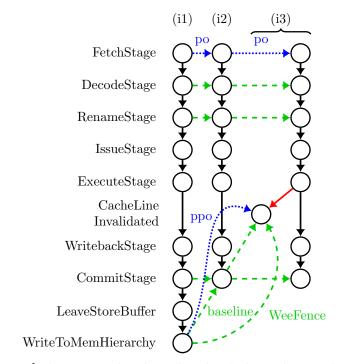

|   |     | 5.7.3   | WeeFence                                         | 140 |

|   | 5.8 | Relate  | ed Work                                          | 141 |

|   | 5.9 | Chapt   | er Summary                                       | 144 |

| 6 | CC  | [Check  | x: Verifying the Coherence-Consistency Interface | 145 |

|   | 6.1 | Introd  | luction                                          | 145 |

|   | 6.2 | Motiv   | ating Example                                    | 148 |

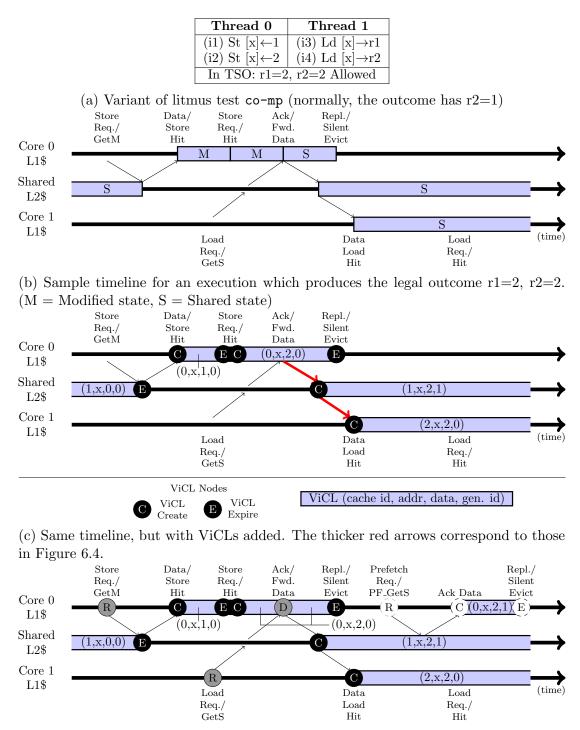

|   |     | 6.2.1   | Coherence-Consistency Interface Mismatches       | 148 |

|   |     | 6.2.2   | The Window of Vulnerability Problem              | 150 |

|   | 6.3 | The V   | ViCL Abstraction                                 | 153 |

|   |     | 6.3.1   | ViCLs: Definition and Usage                      | 153 |

|   |     | 6.3.2   | ViCL Timeline Example                            | 155 |

|   |     | 6.3.3   | Using ViCLs in $\mu$ hb Graphs                   | 157 |

|   |     |         | xiii                                             |     |

|    | 6.4   | CCICł   | neck and $\mu$ hb Graphs                            | 159 |

|----|-------|---------|-----------------------------------------------------|-----|

|    |       | 6.4.1   | ViCL-Aware Microarchitecture Definitions            | 160 |

|    |       | 6.4.2   | Example: A Model with L1 Cache ViCLs Only           | 161 |

|    |       | 6.4.3   | Multilevel Caches                                   | 167 |

|    | 6.5   | Experi  | mental Methodology                                  | 168 |

|    | 6.6   | Case S  | tudies                                              | 169 |

|    |       | 6.6.1   | Partially-Incoherent Caches and L1 Cache Bypassing  | 170 |

|    |       | 6.6.2   | Lazy Coherence                                      | 172 |

|    |       | 6.6.3   | Window of Vulnerability/Peekaboo                    | 175 |

|    |       | 6.6.4   | Performance Results                                 | 178 |

|    | 6.7   | Relate  | d Work                                              | 180 |

|    | 6.8   | Chapte  | er Summary                                          | 182 |

| 7  | Con   | clusior | n and Future Directions                             | 183 |

|    | 7.1   | Future  | Directions                                          | 183 |

|    |       | 7.1.1   | Further Extensions of PipeCheck                     | 183 |

|    |       | 7.1.2   | Formal Correctness Proofs                           | 185 |

|    | 7.2   | Thesis  | Conclusions                                         | 186 |

| A  | Gal   | lery of | MOST-based Definitions for Well-Known Architectures | 190 |

| в  | Gal   | lery of | Shim FSMs                                           | 195 |

| Bi | bliog | graphy  |                                                     | 249 |

## Chapter 1

## Introduction

## 1.1 Motivation

Over the second half of the twentieth century, general-purpose computing developed from a theoretical exercise into a practical and ubiquitous reality. In 1936, Alan Turing invented what is now called a universal Turing machine, an idea which is now widely considered as the theoretical basis for the modern notion of a computer [Tur37]. ENIAC, cited by many as the world's first fully-digital general-purpose computer<sup>1</sup>, was publicly unveiled in 1946 [EM]. The first stored-program computer, the Manchester Small-Scale Experimental Machine, ran its first program in 1948 [Cen15]. The first commercially-available general-purpose digital computer, the Ferranti Mark 1, was purchased in 1951. By the end of the century, fundamental technology advances such as the bipolar transistor, the integrated circuit, CMOS logic, and corresponding advances in software and design technologies drove computing from being a niche application into the commodity that it remains today.

The first half-century of digital computing followed a number of remarkable trends. Gordon Moore, based on a few early observations, predicted in 1965 that transistor

<sup>&</sup>lt;sup>1</sup>Other competitors for this or similar claims include the Atanasoff-Berry Computer, the Colossus Machine, and the Z3 [Com15]. I acknowledge my personal bias towards ENIAC, if only because I received by bachelor's degree from the University of Pennsylvania, where ENIAC was created.

density would double roughly every two years [Moo65]. This phenomenon, popularly dubbed Moore's Law, combined with improvements to the architectures of the processors themselves to lead to a doubling of performance roughly every 18 months. Likewise, Dennard et al. observed in 1974 that by scaling supply voltage downwards with transistor area, transistor power density would be roughly constant [DGY<sup>+</sup>74]. Dennard scaling, together with Moore's law, allowed for high levels of integration, giving high performance at manageable power. Although these trends were generally extrapolated from no more than a few data points, each remarkably held true for decades, leading them to be popularly classified as "laws" and to guide the progress of the semiconductor industry for nearly half a century.

Unfortunately, in the early 2000s, computing hit the power wall [BC11, KM08, SKM15]. Dennard scaling started to break down around 2005, as the power consumption and thermal dissipation requirements of increasingly smaller and faster transistors became impossible to satisfy. This breakdown brought about an end to the exponential growth in single-core performance seen during the previous decades, and it drove the industry to shift to *multicore processors* as a way to deliver continued processor performance scaling [ABC<sup>+</sup>06, HM08]. The ability to extract and make efficient use of parallelism hence became a prerequisite for making the most use of the hardware. Multicore processors are now found throughout most major segments of the industry, from mobile devices to laptops and desktops to supercomputers.

As a consequence of the paradigm shift to multicore processors, *shared memory* parallelism has taken on renewed importance. While software parallelism models can (and do) vary widely, at a hardware level, the predominant paradigm is for the cores in a multicore processor to synchronize and communicate data by reading and writing into a shared memory space. This communication and synchronization takes place according to the *memory consistency model*: the set of rules specifying how and when accesses made by each core become visible to other cores. Unfortunately, the process

of building consistency models and synchronization primitives that are correct, highperformance, and easy to use has proven notoriously difficult over the decades, and so memory models remain the subject of ongoing research even today.

Lamport defined sequential consistency (SC), the first explicit memory consistency model, in 1979 [Lam79]. Sequential consistency (then and today) represents the most intuitive model of shared memory concurrency. It states, roughly, that concurrent programs behave as if they were a single-threaded program formed by interleaving the instructions from each thread. SC was notable for formalizing the rules that many programmers were implicitly assuming about the behavior of parallel programs, particularly in light of the fact that even then, concurrent hardware did not always enforce SC. Today, most computer architects consider the performance of sequentially consistent processors to be too low to be commercially competitive. In modern processors, the requirements of sequential consistency are routinely violated by hardware optimizations such as memory access reordering and store buffering [AMD13, ARM13, IBM13, Int10, Int13a].

In 1986, Dubois et al. proposed the idea of defining a *weak memory model*—one which is weaker (i.e., more permissive) than SC [DSB86]. Weak memory models present a different (usually more complicated but higher-performance than SC) set of rules for shared memory communication. In this approach, the burden of building correct communication and synchronization primitives is shifted onto the programmer and/or the programming language, as either or both must be able to understand and reason about the increasingly complicated set of rules governing cross-core communication.

In spite of the significant added complexity that weak memory models bring, nearly all modern multicore processors implement some form of weak memory model. The shift of computing into the multicore era drove a renewed practical interest in memory consistency model research in the 2000s, and this led to efforts to improve and formalize the memory models used by C/C++ [BA08], Java [MPA05], x86(-64) [OSS09a], and Power [AMT14, MHMS<sup>+</sup>12, SSA<sup>+</sup>11], among others. However, numerous challenges remain. On one hand, memory model analyses following a formal mathematical approach are sufficiently challenging that they tend to take place on the timeframe of years, rendering them unable to fully adjust to the fastmoving world of computing. On the other hand, with every advance in the scientific understanding of memory models comes another discovery that some existing model or framework is broken, thereby revealing just how challenging these problems are [ABD<sup>+</sup>15, ND13, VBC<sup>+</sup>15].

Although memory models have been studied for decades, two contemporary trends in computer architecture are further increasing the difficulty of specifying and reasoning about memory consistency models. First of all, many modern systems are architecturally heterogeneous—they contain processor cores and/or other components which have varying instruction sets and therefore, usually, varying memory consistency models. The GPGPU paradigm, in which a graphics processing unit (GPU) performs general-purpose (GP) computation in collaboration with a CPU, is one notable example, but mobile systems-on-chip (SoCs) may contain as many as a half dozen different components with different instruction sets and MCMs [Qua15, Tex10]. Second, the traditional abstractions of programming language, architecture, and microarchitecture are becoming increasingly blurred. Intermediate representations such as Java bytecode and LLVM IR are increasingly commonly being used as semi-permanent representations of code, and "virtual instruction sets" such as NVIDIA PTX [NVI13b] and HSAIL [HSA13] are diminishing the dominance of any one particular hardware instruction set. Concurrent with this trend is an increase in the popularity of dynamic just-in-time (JIT) compilers [NVI13a, Khr], optimizers [NVIb], and binary translators [DVT12, VT14], cases for which the memory consistency implications have not been as widely studied. These two trends show the importance of having memory consistency model analysis techniques which are flexible enough to adapt to such rapidly-changing conditions.

This thesis bridges the gap between the benefits of rigorous formalism and the need for practical applicability in memory model analysis, all while addressing the recent trends discussed above. The next section describes some of the key challenges that arise in this space, and it lays out the specific goals for this thesis.

### **1.2** Research Challenges and Goals

The past three decades have shown that specifying and reasoning about weak memory models is extremely difficult and prone to numerous pitfalls and unexpected corner cases. In fact, it remains a challenge even to precisely and completely define models such as C++, Java, ARM, or Power which are nevertheless in widespread use. Furthermore, since the software memory model needs to be implemented in terms of the hardware memory model of the processor on which it will execute, the job of building tools such as compilers in a way that correctly accounts for memory models is itself a significant additional challenge [BMO<sup>+</sup>12, VBC<sup>+</sup>15].

Existing approaches and models are insufficient in various ways. For example:

- They are imprecise: many industry specifications are written in natural language and are often too vague to be used to analyze certain cases [AMD13, ARM13, IBM13, Int13a, NVI13b].

- They are incomplete and/or incompatible: e.g., there are cases in which various recent formalizations of the Power memory model disagree with each other [SSA<sup>+</sup>11, MHMS<sup>+</sup>12, AMT14].

- They are impractical and/or inaccessible: e.g., the Java memory model is considered by many to be difficult to use in practice due to its "replay" approach to deriving valid executions [PVJ15].

They are unsound: e.g., numerous early iterations of the C++, Java, and Power memory models were shown to disagree with the realities of the underlying implementations [Alg12, BOS<sup>+</sup>11, SSA<sup>+</sup>11, ŠA08] and each model continues to be refined even today [Bat04, BMO<sup>+</sup>12].

As a result of the above shortcomings, it remains difficult to analyze the memory consistency model implications of building new microarchitectures, toolchains, and programming languages. Even when model definitions exist, they may not be practical to use. For one thing, nearly all existing models are, by necessity, abstracted somewhat from the full realities of the microarchitecture. For another, userfriendly tools which allow non-experts to analyze the memory model behavior are often either non-existent [MHMS<sup>+</sup>12] or prone to state space explosion [SSA<sup>+</sup>11]. As a result, determining correct and optimal mappings for critical standard data structures onto weak memory models remains an active area of research even today [BMO<sup>+</sup>12, LGCP13, LPCZN13].

An additional ongoing challenge is to ensure that hardware being built and shipped to customers is correct with respect to its specification. There have been numerous (in)famous examples of bugs appearing in all parts of the processor, and the memory system is no exception. Although the memory consistency model is more precisely and formally defined than many other components of the processor design, the tools which allow these formalisms to be applied to practical microarchitectural use cases are still not sufficiently developed. This fact leads bugs such as those in implementations of transactional memory [Int15], load-load reordering [ARM11, Elv], or fences [ABD<sup>+</sup>15] to continue to appear in hardware even today. The trend towards increased architectural heterogeneity and the blurring of abstractions in the hardware-software stack will only serve to make these problems more challenging.

In response to the above challenges, this thesis focuses on specifying, verifying, and translating between memory consistency models. It does so in a way that bridges the gap between formal analysis methods and practical microarchitectural use cases. In particular, it applies rigorous methodologies to the analysis of microarchitecturallyimportant cases such as out-of-order execution, speculative reordering, partially incoherent caches, virtual-to-physical address translation, and coherence protocols which violate the formal specifications of coherence. It also builds practical tools which can be used to analyze both currently relevant and forward-looking use cases. The rest of this chapter outlines the approach taken to overcome the challenges and to solve the goals described above.

# 1.3 Defining Memory Models in an Architecture-Independent Manner

One shortcoming of existing approaches to defining memory models is that in general, two unrelated memory models cannot easily be directly compared. In the best case, the two models may each be specified using some precise formalism, but unless the two formalisms use matching approaches and notations, it is difficult or impossible to simply take a component from one model and map it into the language of the other. Instead, the process of deriving a correct mapping between two models generally requires either a conservative over-approximation or a custom third formalism consisting of manual proofs that often take years to complete [BMO<sup>+</sup>12, LPCZN13, SMO<sup>+</sup>12]. This fact makes it difficult to reliably build compilers, dynamic binary translators, or any other mechanism which has to perform such cross-model mappings.

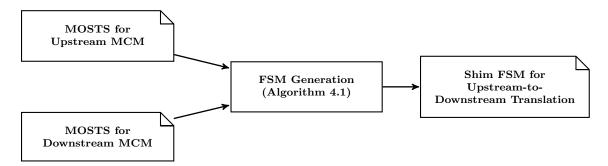

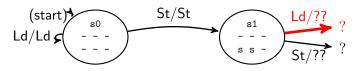

Chapter 3 presents the Memory Ordering Specification Table (MOST), an architecture-independent and model-independent specification format for memory models [LTPM15a, Lus15]. MOSTs provide a precise, self-contained notation for defining the memory ordering requirements or enforcements of the various individual components of a memory model. MOSTs describe preserved program order (PPO, i.e., the set of orderings enforced by hardware by default), fences, inter-instruction dependencies, and all other forms of ordering mechanism used by a model. Taken together, the MOSTs for each individual component collectively form the definition of the memory model in question.

The benefit of the MOST specification format is that by providing a common model-independent language, any two MOSTs can be compared to each other, even when the MOSTs originate from unrelated memory models. In addition to MOSTs themselves, Chapter 3 also presents the ArMOR framework, a primitive "arithmetic" on MOSTs which can be used to analyze, compare, and manipulate MOSTs. Ar-MOR enables MOSTs to be flexibly applied in compilers, dynamic translators, and other interesting use cases. The ArMOR framework is released as an open-source tool [Lus15].

#### **1.3.1** Dynamic Migration Between Consistency Models

A key benefit of the ArMOR framework is that it enables new memory consistencyrelated use cases which were not previously feasible to build. Chapter 4 highlights the example of dynamic binary translators (DBTs) that translate between different instruction set architectures (ISAs) [LTPM15a]. Although cross-ISA binary translation has been shown to deliver performance and/or energy benefits, existing frameworks simply do not address the memory consistency implications of doing so [DVT12, VT14]. Likewise, existing architectural emulators such as the Android emulator and QEMU implement single-threaded backends in order to simply avoid the memory model issue altogether [Goo15, Qem15].

Chapter 4 presents an in-depth case study of using MOSTs and the ArMOR framework to build memory-model-aware dynamic binary translators. Given the set of MOSTs defining the source and target memory models, this chapter presents an algorithm for automatically deriving *shims*, or small, self-contained translation modules which automatically insert fences or other ordering mechanisms as needed. This chapter demonstrates that both software and hardware shim implementations have low to negligible performance overheads, making them practical to implement. The appendix to this thesis also presents a gallery of shims for different scenarios. The code used to generate this appendix is open source as well [Lus15]. The chapter concludes by considering extended use cases such as optimization via dynamic removal of redundant fences and by presenting a broader view of the ways in which future architectures can make the analysis and implementation of such technologies easier.

# 1.4 Microarchitecture-Level Memory Consistency Models

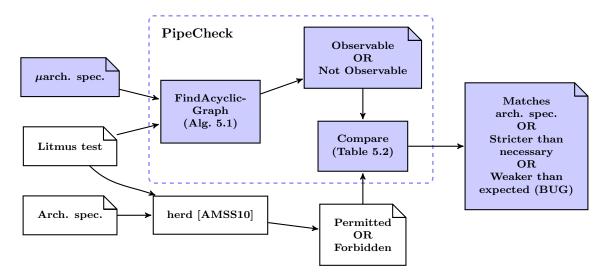

Even though hardware memory models are intentionally abstracted from the details of any one particular implementation, they are often nevertheless inspired by some class of microarchitectural features. For example, microarchitectural store buffering inspired the design of processor consistency and SPARC total store ordering (TSO), and some models contain explicit references to microarchitectural features such as branch prediction [SSA<sup>+</sup>11, PVJ15]. Nevertheless, the models are intentionally designed to be portable across varying implementation for the sake of backward/forward compatibility: a memory model may be implemented by more than one company (e.g., TSO by SPARC/Oracle [SPA94b], Intel [Int13a], AMD [AMD13], and others) and/or by more than one chip produced by the same company (e.g., Intel Haswell/Broadwell "big cores", Bonnell/Silvermont "small cores"). This fact means that by design, existing models cannot specify behaviors specific to any one implementation. As a result, existing frameworks cannot generally be applied either to microarchitectural verification or to scenarios such as modern GPUs which do not have well-defined architecture-level memory model specifications. Chapter 5 introduces PipeCheck, a methodology and open-source tool for verifying the correctness of a given microarchitecture against a given architecture-level memory model specification [LPM14, LPM15, Lus14]. PipeCheck provides a domainspecific language (DSL) for defining a multi-event axiomatic model of the memory consistency behavior of one particular microarchitecture. It uses this model to quickly and automatically identify cases in which the microarchitecture may be stricter than necessary (e.g., an SC implementation of TSO) or weaker than necessary (e.g., due to an implementation bug).

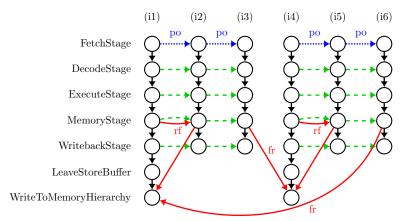

Specifically, PipeCheck defines the memory ordering behavior of a pipeline using a set of microarchitecture-specific ordering axioms: some defining per-instruction behavior, some defining per-pipeline stage behavior, and some defining other relevant ordering enforcement behaviors. For example, an axiom may state (using more formal language) that "the decode stage is FIFO" or that "a load may either take a cache hit, take a cache miss, or forward from the store buffer". PipeCheck then determines whether any executions which violate the architecture-level specification are observable in terms of the axioms provided. The axioms are designed with the intention that, to the extent possible, they can be verified and analyzed entirely independently. In this way, the PipeCheck methodology as a whole therefore reduces the burden of verifying a particular pipeline as a whole to the more tractable problem of verifying the localized behaviors of individual pipeline stages or events.

There are numerous microarchitectural components which play a role in memory ordering: the pipeline, the cache hierarchy, the address translation mechanisms, the networks-on-chip (NoCs), and so on. The analysis of various microarchitectual subsystems using the PipeCheck methodology is organized as described below.

#### 1.4.1 Pipeline Models

Chapter 5 focuses on the role of the pipeline itself in enforcing the memory consistency model [LPM14, LPM15]. The memory hierarchy itself often provides little to no ordering guarantees beyond some form of *cache coherence*, leaving the pipeline largely responsible for enforcing consistency guarantees. Likewise, fences or other explicit ordering mechanisms are generally enforced within the pipeline itself; such mechanisms do not often propagate explicitly to the memory system. Nevertheless, the pipeline may itself contain a number of performance optimizations which may themselves introduce weak memory behavior. Chapter 5 therefore demonstrates how to verify pipelines containing optimizations such as of out-of-order execution, speculative load reordering, or other similar mechanisms.

#### 1.4.2 Cache and Memory System Models

While Chapter 5 abstracts away much of the behavior of the cache hierarchy, Chapter 6 highlight ways in which specific low-level behaviors of certain cache hierarchies may need to be addressed explicitly [MLPM15]. For example, although most architecture-level memory models contain some formal notion of coherence, there are cases in which particular cache coherence protocols may in fact violate certain interpretations of the word "coherence", as "coherence" is defined in varying ways by different authors. Adding an explicit model of the coherence-consistency interface (CCI) to PipeCheck allows it to verify that the microarchitecture as a whole continues to implement the memory model correctly, given the precise behavior of the coherence protocol.

CCICheck extends the methodology and software implementation of PipeCheck to explicitly model the behavior of a particular cache coherence protocol. CCICheck provides the key innovation of the *value-in-cache-lifetime* (ViCL), an abstraction of the lifetime of a given piece of data being held in a particular cache line in some specific cache. The ViCL abstraction allows CCICheck to explicitly and scalably model behaviors such as cache hits vs. cache misses, incoherent caches, and lazy cache invalidation, and these models allow CCICheck to verify the correctness of each behavior with respect to the memory model. The chapter concludes with an exploration of how CCICheck can be used to verify the correctness of various coherence protocols which have been recently proposed in the academic literature.

#### 1.4.3 Address Translation

A related but less-studied question is the role that virtual-to-physical address translation plays in the specification and verification of memory consistency models. Romanescu et al. [RLS10] brought attention to the fact that problems such as TLB synonyms—two virtual addresses which map to the same physical address—can imply ordering requirements that cannot be inferred from virtual or physical addresses alone. Section 7.1.1 discusses ongoing work to apply PipeCheck to the verification of such scenarios [LSMB15].

### 1.5 Thesis Contributions

This thesis makes an impact via the following significant contributions:

• Inspired by the shortcomings of existing informal memory consistency model specification techniques, this thesis defines the Memory Ordering Specification Table (MOST), a precise, self-contained notation for defining components of a memory consistency model [LTPM15a]. MOSTs improve upon existing specification formats by directly including features (e.g., fence cumulativity and degree of store atomicity) that are left unaddressed by simpler models. The key contribution of MOSTs is that they eliminate much of the imprecision found in

typical industry definitions of memory consistency model behaviors and hence also of the analyses that make use of such definitions.

- To demonstrate the practical value of MOSTs, this thesis also presents the open-source ArMOR framework for systematically analyzing and manipulating MOSTs [Lus15]. The precision and completeness of MOSTs allows them to be analyzed to improve the rigor of use cases which already exist (e.g., compilers) and in use cases which are forward-looking (e.g., cross-ISA dynamic binary translation). This thesis performs an in-depth analysis of the latter, showing not only that the necessary analysis can be automated using ArMOR, but also that such translation can be made practical in a variety of hardware and software scenarios.

- The work in this thesis is the first to present a general-purpose formal axiomatic memory model framework for specifying and verifying microarchitectural memory access reordering behavior [LPM14, LPM15]. While previous work had shown the need for rigor and formalism when analyzing memory consistency models at the architecture or software level, no previous work had applied such techniques to the microarchitecture space. PipeCheck's microarchitectural happens-before (µhb) graphs and the domain-specific language (DSL) that defines how they are enumerated provide a clear, visualizable approach for specifying and verifying implementation-level memory reordering optimizations.

## 1.6 Thesis Outline

The rest of this thesis is organized as follows. Chapter 2 presents a background of history and current practice of memory consistency models. Chapter 3 introduces the MOST specification format and the ArMOR framework for systematically manipulating MOSTs. Chapter 4 then presents an in-depth case study of the use of MOSTs to perform flexible and practical cross-ISA dynamic binary translation. Chapter 5 introduces PipeCheck, a methodology and automated tool for defining and analyzing microarchitecture-level consistency models, while focusing on the behavior of the pipeline itself. Chapter 6 then develops a microarchitecture-level model for verifying the consistency implications of cache coherence protocols. Finally, Chapter 7 presents ongoing and future research directions and then concludes this thesis.

## Chapter 2

## **Background and Related Work**

This chapter presents an overview of past and ongoing research in the field of memory consistency models. This overview serves as the foundation for the rest of this thesis. Section 2.1 presents high-level background on memory consistency models in general, and Section 2.2 describes the approaches most often used to define weak memory models. Section 2.3 explains how empirical methods are used to complement formal analyses in practical usage scenarios. Section 2.4 discusses some challenges faced when trying to compare or map between different memory models. Section 2.5 describes some simplifying assumptions that we make in this thesis, in keeping with other related work on memory consistency models. Section 2.6 then concludes.

## 2.1 Basic Overview

A memory consistency model is defined by Adve and Gharachorloo as follows [AG96]:

[A] memory consistency model [...] provides a formal specification of how the memory system will appear to the programmer, eliminating the gap between the behavior expected by the programmer and the actual behavior supported by a system. Effectively, the consistency model places restrictions on the values that can be returned by a read in a sharedmemory program execution.

The most intuitive way to define a memory model is to state that each load is required to return the value of the latest store to the same address. This works in singlethreaded code, because "latest" can be defined as the most recent such store in *program order*: the order in which the instructions were originally laid out in the code being executed. In multithreaded programs, however, accesses from other cores may be interleaved with the accesses of the core in question. This means that there will in general be many values that any given load might plausibly return. The goal of a memory model is therefore to specify which values are legal to return and which are not.

A naive approach to defining the multithreaded sense of "latest load" is to choose the store (originating from any core in the system) that has happened most recently in an absolute physical sense. This is sometimes known as *strict consistency*. However, global synchronization or coordination among a distributed set of cores is difficult or even impossible to implement in practice, as any inter-core communication or synchronization requires passing of messages which themselves take non-trivial (and often unpredictable) amounts of time to propagate. Strict consistency is therefore considered infeasible to implement in practice. In practical models, "latest" must therefore be defined in such a way that it does not refer to any notion of a global physical timeline.

#### 2.1.1 From Sequential Consistency to Weak Ordering

The first memory consistency model, *sequential consistency* (SC), was defined in 1979 by Lamport [Lam79]. SC was originally defined in terms of two properties:

1. The result of any execution is the same as if the operations of all the threads were executed in some sequential order. 2. The operations of each individual thread appear in this sequence in the order specified by the thread.

The key benefit of SC is that it closely matches programmers' intuitions about how multithreaded programs should behave. Under SC, for each load, the set of values that can be returned consists of exactly one element: the most recent store to the same address, according to the interleaving implied by rule 1.

In spite of its intuitiveness, Lamport noted in his paper that enforcing sequential consistency "may not be worth the price of slowing down the processors" [Lam79]. In fact, nearly all modern systems intentionally sacrifice the elegance of SC to deliver higher performance. Memory accesses may be *reordered* from how they originally appear in the code into an order that improves latency and/or throughput, thereby violating rule 2 of SC. Furthermore, accesses may be *buffered* in ways that make them visible to certain threads before they become visible to other threads. This causes different threads to potentially observe the same set of events occurring in different orders, thereby violating rule 1 of SC.

Weak memory models legalize the reordering of memory accesses, buffering of memory accesses, and lack of global consensus. Weak models have been defined in various ways over the years. Dubois et al. first defined them as follows [DSB86]:

In a multiprocessor system, storage accesses are weakly ordered if 1) accesses to global synchronizing variables are strongly ordered and if 2) no access to a synchronizing variable is issued in a processor before all previous global data accesses have been performed and if 3) no access to global data is issued by a processor before a previous access to a synchronizing variable has been performed.

Here, synchronizing variables are variables which are explicitly declared as such by the programmer. Strong ordering is a concept that has been found to be too weak; most modern definitions replace "strongly ordered" in the above definition with "sequentially consistent". Finally, "perform" is defined by the authors as follows:

A LOAD by processor I is considered performed with respect to processor K at a point in time when the issuing of a STORE to the same address by processor K cannot affect the value returned to processor I. A STORE by processor I is considered performed with respect to processor K, at a point in time when an issued LOAD to the same address by processor K returns the value defined by the STORE. An access by processor I is performed [(or globally performed)] when it is performed with respect to all processors.

Some memory models use the same definition of "perform" to this day [IBM13]. However, it has proven difficult to formalize, as the loads and stores to which the definition refers are hypothetical: they may not (and in general do not) actually exist, thereby making it hard for formal analyses even to refer to them. Chapter 5 addresses this problem and presents a microarchitecturally-inspired solution.

In response to the above shortcomings in the Dubois et al. definition, Adve and Hill proposed an alternative definition of weak ordering that by design focused on outcomes rather than mechanisms [AH90]:

Hardware is weakly ordered with respect to a synchronization model if and only if it appears sequentially consistent to all software that obey[s] the synchronization model.

To go along with this definition, they also propose the now widely-used *data-race-free* (DRF) family of synchronization models. DRF rules state that all conflicting accessses (i.e., accesses from different cores to the same address and for which at least one is not a read) must be ordered by a happens-before relationship induced by explicit synchronization operations on the cores in question.

In modern informal usage, any memory model which violates either of the two rules of SC may be considered "weak" or "relaxed". The Adve and Hill definition of weak ordering focuses on the ability of a processor to restore sequential consistency, and most modern architectures do satisfy this requirement. However, modern usage frequently diverges from the Adve and Hill definition in two key ways. First, their definition technically requires synchronization operations to access memory, while modern hardware more commonly performs synchronization using fences or other mechanisms which do not themsleves access memory. Second, and more fundamentally, a large body of modern research in memory models explicitly focuses on behaviors which are not sequentially consistent as the explicit area of interest, even though these behaviors are explicitly forbidden under the Adve and Hill definition [Adv93]. Essentially all modern hardware uses a model weaker than SC, and many performance-critical data structures are carefully and explicitly optimized to take advantage of the performance benefits of non-SC behavior [BMO<sup>+</sup>12, LGCP13, LPCZN13, MRP<sup>+</sup>14]. This thesis primarily falls within this context of properly specifying and verifying behaviors which are desirable even though they are not sequentially consistent.

Even from the beginning, Lamport cautioned that when designing synchronization protocols "at the lowest level of the machine code" (i.e., on non-SC machines), "verifying their correctness becomes a monumental task" [Lam79]. Today, weak memory models are often considered highly counterintuitive and difficult to work with, and software models often make it a goal to hide such behavior from the user when it does exist [BA08, MPA05]. Nevertheless, since non-SC behavior is in widespread use at both the hardware and the software levels, a proper understanding of weaker-than-SC memory models is crucial to the correctness of modern systems.

| Layer                          | Notable Modern Examples                                                                              |

|--------------------------------|------------------------------------------------------------------------------------------------------|

| Software                       | C++ [BA08], Java [MPA05]                                                                             |

| Intermediate<br>Representation | HSAIL [HSA13], LLVM IR [LA04],<br>NVIDIA PTX Virtual ISA [NVI13b]                                    |

| Architecture                   | SC [Lam79], x86-TSO [OSS09a],<br>IBM Power [AMT14, MHMS <sup>+</sup> 12, IBM13, SSA <sup>+</sup> 11] |

| Microarchitecture              | (this thesis)                                                                                        |

Figure 2.1: A stack of memory models. Each builds on top of the layers below it.

#### 2.1.2 A Stack of Memory Consistency Models

Just as in many other computing disciplines, memory models are generally built in multiple layers. Hardware-level memory models provide a layer of abstraction across different microarchitectural implementations. Software-level memory models then provide a layer of portability across different hardware models. Other layers (e.g., compiler intermediate representations) may be used as well. Figure 2.1 provides some examples relevant to systems in use today. Each layer must be implemented in terms of the layer below it in the stack. Note that much of this complexity is often hidden inside compilers, libraries, or other similar tools.

Prior to this thesis, most research into formally specifying and analyzing memory models took place at the architecture level and above. This left a large gap between the high-level architecture specification and the implementation level, and verification within this gap could not be easily performed. As such, this thesis focuses on specifying and analyzing architecture- and microarchitecture-level memory models in an effort to bridge this gap.

#### 2.1.3 Coherence vs. Consistency

Cache coherence is a property that is distinct from yet closely related to and often confused with memory consistency. In this section, we summarize the competing definitions of coherence used by various authors, identify how they relate to consistency, and then state the terminology we will use in the rest of this thesis.

Coherence is defined in many varying ways by different authors; no single definition can be considered universal. One common definition is the property that the accesses to each individual address are sequentially consistent [CLS03]. Many authors use the narrower property that there exists a globally-agreed-upon total ordering on the visibility of stores (but not loads) performed to each address [Alg12, SSA<sup>+</sup>11]. This particular ordering is called *write serialization* (ws). Cache coherence protocols often define coherence in terms of a pair of properties: the Single Writer/ Multiple Reader (SWMR) property says that there may be zero or more read-only copies or exactly one read-write copy (but not both), and the Get Latest Value (GLV) property states that reads to each address return the value of the latest write to that address [SHW11]. Other authors use still other subtly distinct definitions [HP11, MHMS<sup>+</sup>12, MHW03, SSA<sup>+</sup>11]. To avoid confusion arising from competing definitions of coherence, the term "coherence" is not used in this thesis without any other context. Instead, preference is given to more precisely-defined properties such as write serialization, SWMR, and so on.

Perhaps surprisingly, the role of coherence in memory consistency model specifications is still partially unsettled. Nearly all consistency models for multicore CPUs and heterogeneous SoCs (e.g., those with CPUs and GPUs) explicitly require coherence [AMT14, HSA13, MHMS<sup>+</sup>12, NVI13b, OSS09a, SSA<sup>+</sup>11]. In software models, however, the role of coherence is less clear. C++11 did not originally address coherence explicitly [BA08]. However, this omission was later found (during a subsequent academic formalization process) to make the specification unsound [Bat04, BOS<sup>+</sup>11]. C++ now requires coherence in the form of four axioms relating the "happens-before" ordering to the "modification order" [ISO11a]. The current Java memory model does not mention coherence. At the same time, it has not yet been formally analyzed to the same degree as the C++11 model has, and so it is possible that future revisions may need to include it as well.

Many architects consider coherence and consistency to be entirely decoupled concepts [Mar05]. According to this point of view, the job of the cache coherence protocol is simply to enforce orderings between accesses to the same address (i.e., coherence, for some definition of coherence) by correctly responding to requests and/or by stalling requests when necessary. The job of the consistency model is then to enforce orderings between accesses to different addresses. The key benefit of decoupling coherence and consistency is that verification of each part independently becomes dramatically easier. This is reflected in the literature: there are numerous papers on verifying coherence protocols [McM01, SSH<sup>+</sup>13, SKA13, ZLS10, ZBES14] or on verifying consistency while assuming a working coherence protocol [Alg12, AMT14, OSS09a, SSA<sup>+</sup>11], but there are far fewer on verifying coherence and consistency together [GSSVD00, TDF<sup>+</sup>02]. However, many consistency model implementations are tightly interwoven with the coherence protocol implementation to enable performance optimizations such as speculative load reordering [GGH91]. At this level, coherence and consistency inherently cannot always be decoupled, and as Chapter 6 shows, the details of individual coherence protocols can play an important role in enforcing coherence.

The question of how coherence relates to consistency comes up repeatedly in this thesis. Chapter 3 introduces a notation for precisely specifying the orderings that are or are not included in "coherence" for a variety of architectures. Chapter 5 uses an idealized model of memory which enforces only write serialization, but Chapter 6 dives deeper and carefully explores how consistency model implementations depend on write serialization, SWMR, and many other varying properties which may or may not be enforced by any given coherence protocol.

| Τł                | nread 0 | Т    | hread 1              |

|-------------------|---------|------|----------------------|

| st                | [x]←1   | ld   | [y]→r1               |

| st                | [y]←1   | ld   | $[x] \rightarrow r2$ |

| Proposed Outcome: |         |      |                      |

|                   | 1:r1=1  | , 1: | r2=0                 |

| Thread 0                              |                  |  | r | Thread 1 |  |  |

|---------------------------------------|------------------|--|---|----------|--|--|

|                                       | [EAX],<br>[EBX], |  |   |          |  |  |

| Proposed Outcome:<br>1:ECX=1, 1:EDX=0 |                  |  |   |          |  |  |

(a) Architecture-independent version

(b) x86-specific version

Figure 2.2: Litmus test mp.

### 2.1.4 Litmus Tests

Litmus tests are very small programs used to test and/or reason about the behavior of a memory consistency model. Figure 2.2 gives one example. A typical litmus test contains a small number of threads (generally 2-4) each executing a small number of instructions (generally 1-6). The instructions in a litmus test generally consist of explicit loads, stores, fences, or atomic read-modify-write operations. Non-memory instructions are generally omitted, except where relevant to, e.g., establish the presence of an address, control, or data dependency. The initial state of memory is, by convention, that all addresses start holding the value zero unless otherwise explicitly stated. Litmus tests also specify a particular outcome of interest. This outcome specifies the values returned by loads and/or the final value stored at a particular address. If the test is associated with a particular memory model, the test may also specify whether the proposed outcome is *permitted* or *forbidden* by the rules of that model. Such an annotation would serve as a reference during testing.

The instructions in a litmus test are often presented in a way that makes them independent of any particular architecture. In particular, litmus tests often abstract away details of instruction sets, use notation loosely, and so on. This allows the litmus test to focus on the memory model itself, as opposed to the irrelevant details of any one instruction set. It also in many cases allows for one test to be analyzed across a variety of memory models. Litmus tests are used in various ways. First of all, litmus tests are used as a means of allowing humans and computers to reason about a particular behavior of interest. Second, they can provide a concrete complement to definitions which are otherwise incomplete and/or highly abstract. I will use litmus tests in both ways throughout this chapter and the rest of this thesis.

# 2.2 Defining Weak Memory Models

Driven by the need for higher-performance alternatives to SC, much modern research and development into memory consistency focuses on the specification and implementation of weak memory models. Unfortunately, as Lamport so presciently predicted, reasoning about weak memory models (i.e., determining which values may be legally returned by memory loads) is made significantly more difficult by the reordering, buffering, and lack of global consensus described earlier. Here, I provide some background on why these weakly-ordered implementations do not lend themselves to simple descriptions or specifications. Chapter 3 then introduces ways in which memory models can be described while taking these important subtleties into account, and Chapters 5 and 6 then describe how to rigorously analyze this buffering and reordering at the microarchitecture level.

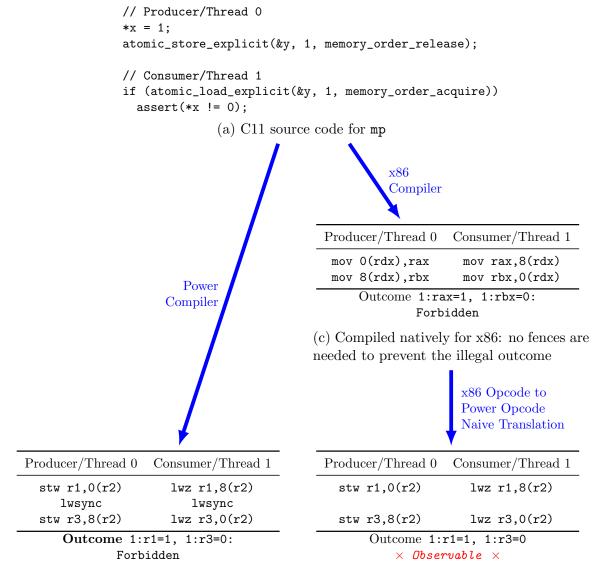

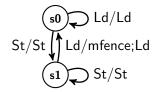

## 2.2.1 Motivating Example

The most prominent property of weak memory models is that, in contrast to rule 2 of sequential consistency, they allow certain program order relationships to be relaxed. The specification of which program order relationships must be globally maintained is called *preserved program order* (PPO). In other words, if (a) comes before (b) in program order, and  $a \rightarrow b$  must be preserved, then (a) must happen before (b) from

|        | Loads      | Stores       | 1 |              | Legend:                      |

|--------|------------|--------------|---|--------------|------------------------------|

| Loads  | Loadis     | √            |   | $\checkmark$ | Ordering preserved           |

| Stores | - (mfence) | $\checkmark$ |   |              | Ordering not preserved       |

|        |            |              |   | (mfence)     | Ordering preserved by mfence |

Figure 2.3: One common (yet incomplete) definition of the total store ordering (TSO) memory model

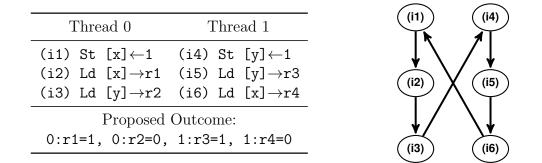

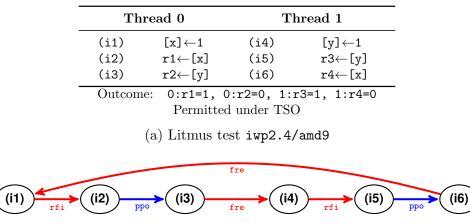

Figure 2.4: Litmus test iwp2.4 demonstrates that proper memory models to be able to both capture and reason about very subtle behaviors

the point of view of every observer in the system. Otherwise, if  $a \rightarrow b$  need not be preserved, some cores may see the effect of (b) before they see the effect of (a).

Preserved program order is often loosely specified using tables such as the one in Figure 2.3. Every cell such a table indicates whether the corresponding types of accesses in program order must be preserved. In this example, Total Store Ordering (TSO) allows for store $\rightarrow$ load reordering, but it forbids other types of reorderings [OSS09a, SPA94b]. The inspiration for TSO is that it allows for the insertion of store buffers between the core and the memory. These store buffers allow loads to bypass earlier stores, thereby improving overall latency. Preserved program order exists across a wide spectrum. Under sequential consistency, all program order relationships must be preserved. Under models such as those used by ARM and Power, few orderings must be preserved, but describing the orderings can be very difficult [AMT14].

Consider litmus test iwp2.4 in Figure 2.4. This particular test is designed to highlight how store buffering introduces behavior that is non-trivial to characterize

and therefore requires non-trivial memory model specification approaches. The focus on store buffering can be seen from the choices of instructions in the threads of the test: because (i1) and (i2) are a write followed by a read to the same address, it is likely (but not strictly required) that (i2) will forward its data from (i1) while (i1) is still in the store buffer. Similarly, (i5) will likely forward from (i4).

Naive happens-before analysis would proceed as follows. Since (i1) is before (i2) in program order and (i2) reads from the value written by (i1), (i1) must happen before (i2). Likewise, (i4) must happen before (i5). If (i4) were to happen before (i3), then (i3) would be forced to return the value 1, contradicting the proposed outcome. Therefore, (i3) must happen before (i4). For similar reasons, (i6) must happen before (i1).

The iwp2.4 litmus test outcome is not legal under sequential consistency, as there is no single ordering in which 1) program order is respected, and 2) all of the above ordering relationships hold. This is depicted by the cycle shown in Figure 2.4. However, in spite of the cycle, and in spite of what Figure 2.3 might imply, the outcome proposed in Figure 2.4 is permitted under Total Store Ordering (TSO). If (i2) and (i5) store buffer forward from (i1) and (i4), respectively, then the edges from (i1) to (i2) and from (i5) to (i6) are effectively "weaker" than the others (in a formal sense), and the cycle loses its effect. Therefore, this type of weakening must be taken into account by the analysis mechanism for TSO (and likewise for other models).

Since naive specification approaches are insufficient, a number of different approaches have been developed in the academic literature and put into use in practice. The next section describes some of these more advanced techniques, and we return to litmus test iwp2.4 in Section 5.3.3.

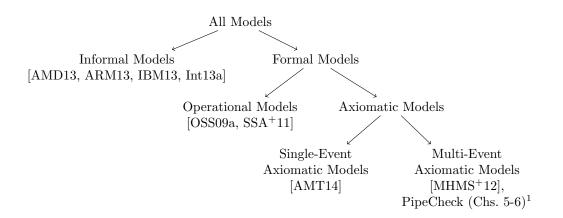

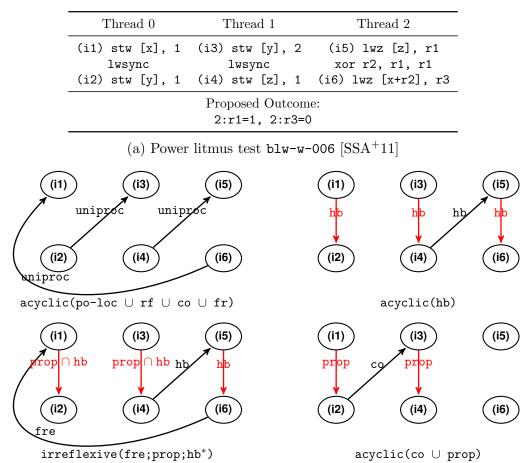

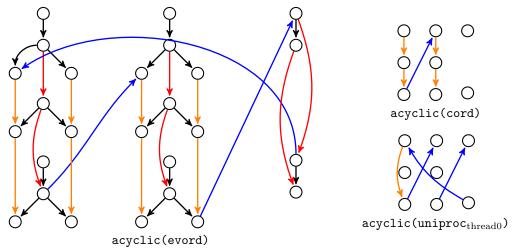

Figure 2.5: A taxonomy of common approaches used to define hardware memory consistency models

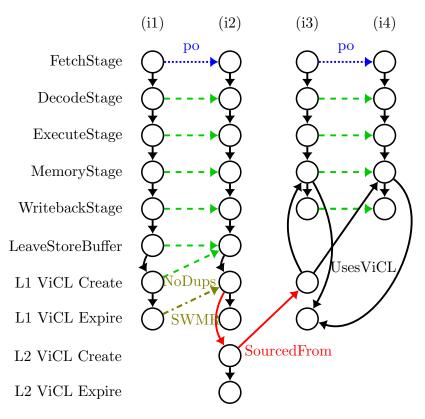

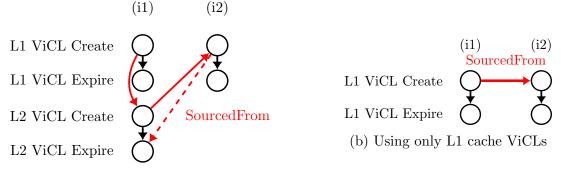

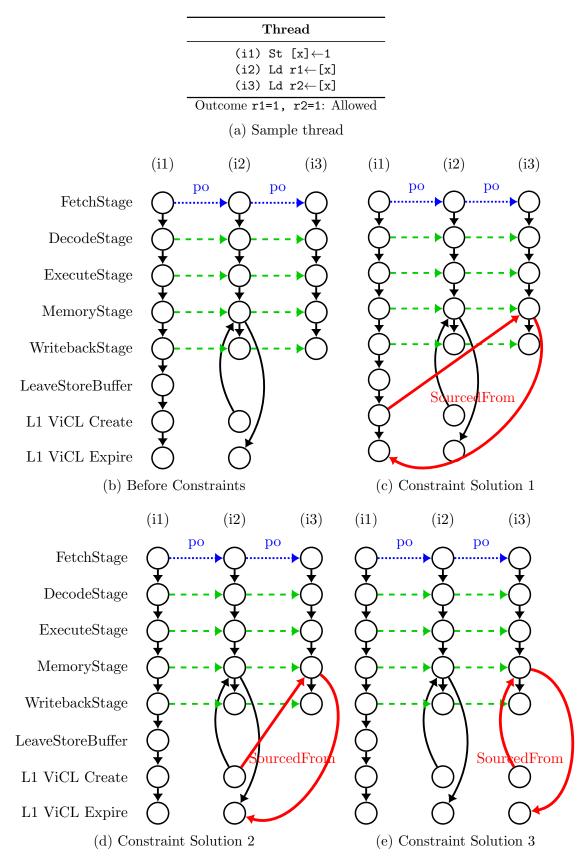

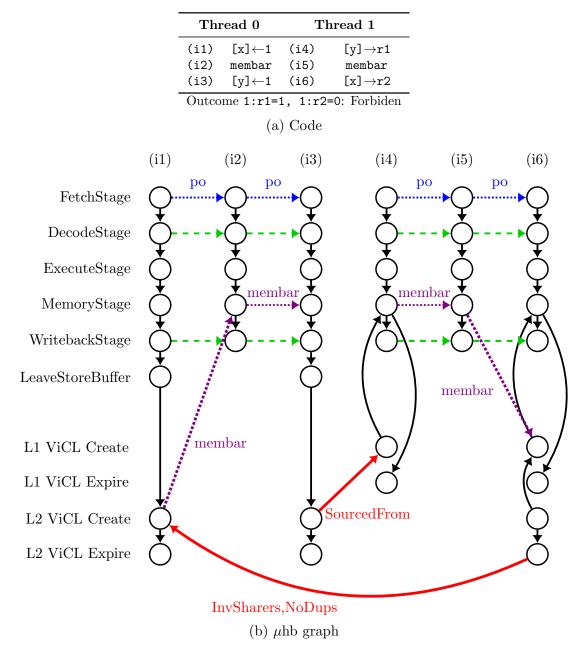

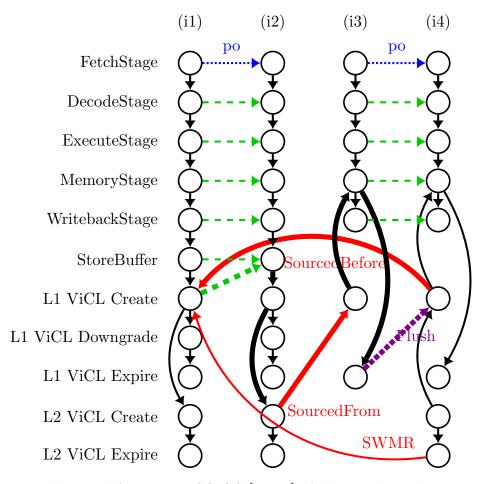

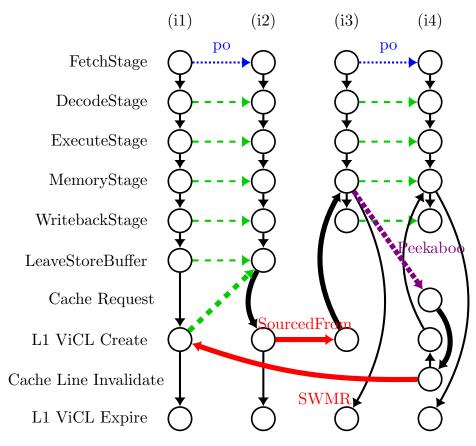

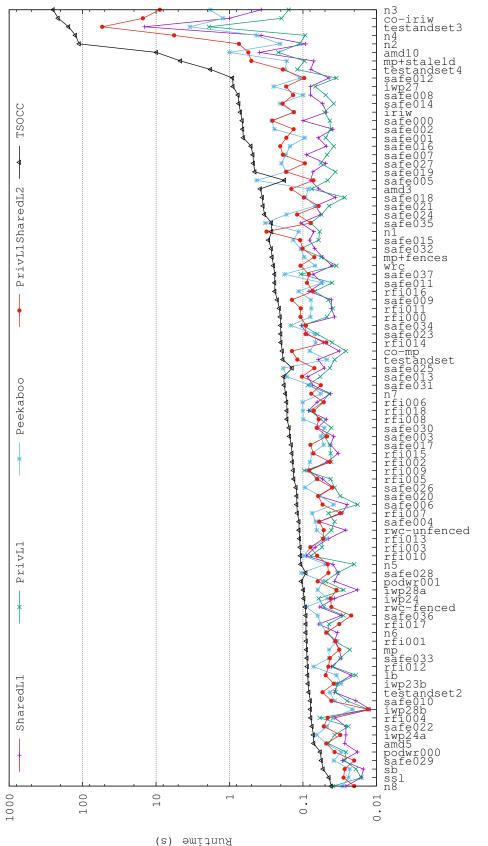

### 2.2.2 Operational vs. Axiomatic Models